在現代電子技術領域,綜合電路圖和集成電路是兩個緊密相連且至關重要的概念。它們共同構成了電子設備設計和制造的基礎,從智能手機到航天器,無不依賴于它們的精確實現。本文將深入探討綜合電路圖與集成電路的定義、功能、發展歷程以及它們在當今科技中的應用。

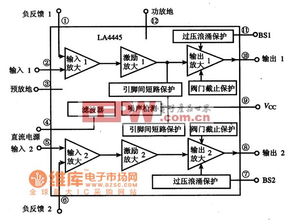

綜合電路圖是一種圖形化的設計工具,用于表示電子系統中各個組件之間的連接關系和功能邏輯。它通常包括電阻、電容、晶體管等基本元件,并通過線條展示電流路徑。綜合電路圖不僅是工程師溝通設計意圖的通用語言,還是仿真和測試電路性能的關鍵依據。在電子設計自動化(EDA)工具的輔助下,綜合電路圖可以優化布局,減少錯誤,提高設計效率。

集成電路,則是指將多個電子元件(如晶體管、二極管和電阻)集成在一塊半導體材料(通常是硅)上的微型電路。自20世紀50年代末發明以來,集成電路經歷了從小規模集成(SSI)到超大規模集成(VLSI)的演進,如今已發展到納米級別。集成電路的優勢在于其小型化、高可靠性和低成本,這使得電子設備能夠實現復雜功能,同時保持緊湊的尺寸。例如,現代微處理器和內存芯片都是集成電路的典型代表。

綜合電路圖與集成電路的關系密不可分。在集成電路的設計過程中,工程師首先需要繪制綜合電路圖來定義電路的結構和行為。這個階段包括邏輯綜合和布局布線,確保電路在物理層面能夠高效實現。一旦設計完成,綜合電路圖便被轉換為掩模圖,用于半導體制造。最終,通過光刻和蝕刻等工藝,集成電路被生產出來。因此,綜合電路圖是集成電路從概念到實物的橋梁。

隨著科技的進步,綜合電路圖和集成電路的發展也面臨新的挑戰和機遇。例如,人工智能和物聯網的興起推動了對更高效、低功耗集成電路的需求,這要求綜合電路圖設計時考慮更多因素,如功耗管理和信號完整性。同時,新興技術如量子計算和柔性電子學正在重塑集成電路的未來,可能需要全新的綜合方法。

綜合電路圖和集成電路是電子工程的核心支柱,它們不僅推動了數字革命,還持續賦能創新。對于工程師和科技愛好者而言,理解它們的基本原理和應用,是掌握現代技術的關鍵。隨著材料科學和計算能力的提升,我們將看到更智能、更集成的電路系統,進一步改變人類生活。